TM 5-6675-318-14

(c) Six clock periods are necessary for the microprocessor to accom-

p l i s h a READ from memory, interpret and perform the instruction. Four more clock

p e r i o d s are required to complete a WRITE from the microprocessor to RAM on PCA A4 or

a register on PCA A2 or A5.

NOTE

In order to troubleshoot hardware failures in the processing circuits,

it is necessary to follow the function of the circuitry in terms

See Table

of ROM phase timing when performing READ and WRITE operations.

3-6 which relates the timing operation of the processing circuits.

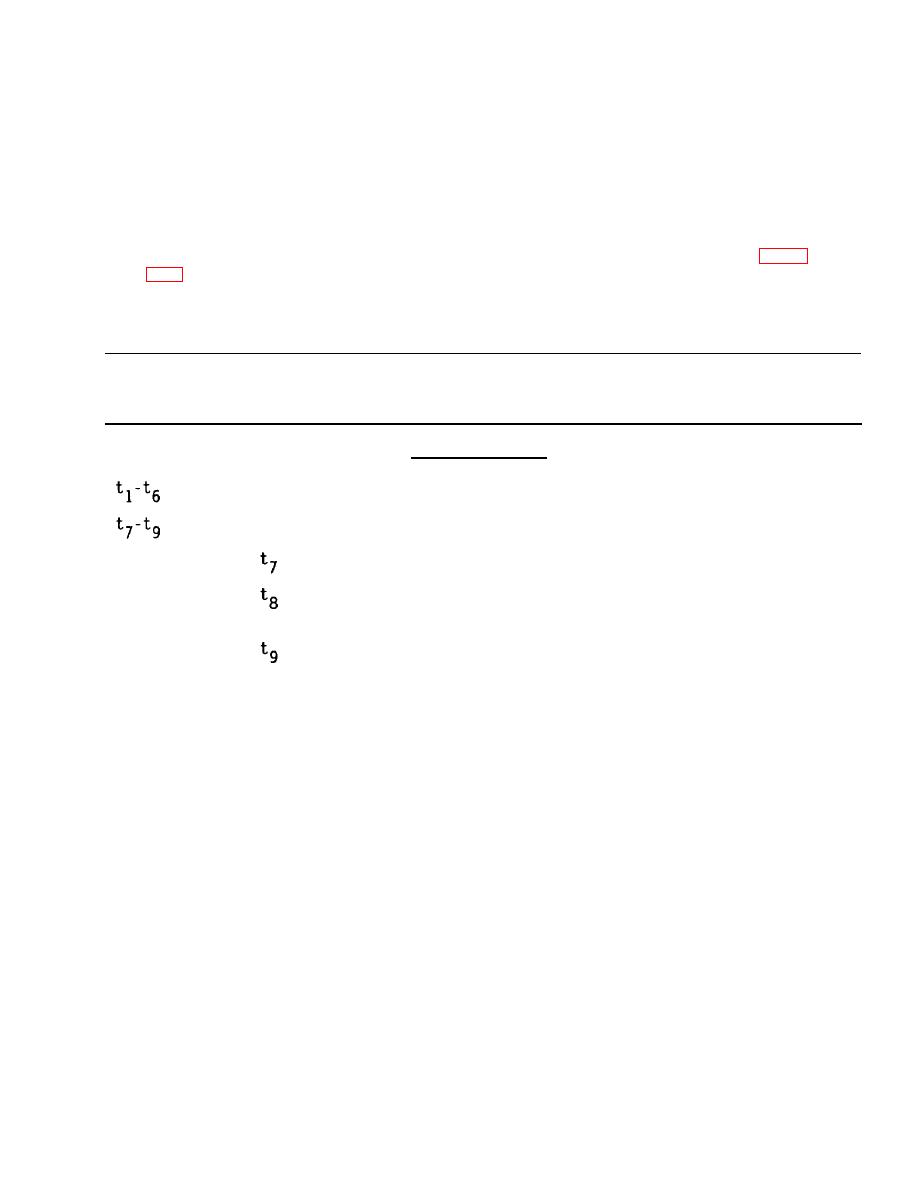

PROCESSING CIRCUITS FUNCTIONAL SEQUENCE OPERATION

Clock

Operation of Circuit

Period

WRITE OPERATION

Microprocessor tells RAM in which address to store data.

Data is transferred to be stored as follows:

M i c r o p r o c e s s o r sets READ to low producing a high WRITE.

s t a r t memory (STM) goes high which tells memory to stand by to

receive data.

e x t e n d e d synchronous memory complete (EXSMC) is generated.

Directs microprocessor to place data on data bus.

Microprocessor can also send data (write) to any of the following:

R e g i s t e r s on I/O Interface PCA A2

Registers on HP-IB PCA A2

S e l f - t e s t registers on PCA A3

I n t e r r u p t registers on PCA A3

P r o c e s s of writing data to one of these other locations is accom-

plished in similar manner as described above. Correct register is

deactivated by register decoder which decodes data bits -4.

A 5 card decoder is activated by I/O RAC, which is produced by

register decoder.

3-23