TM 5-6675-316-14

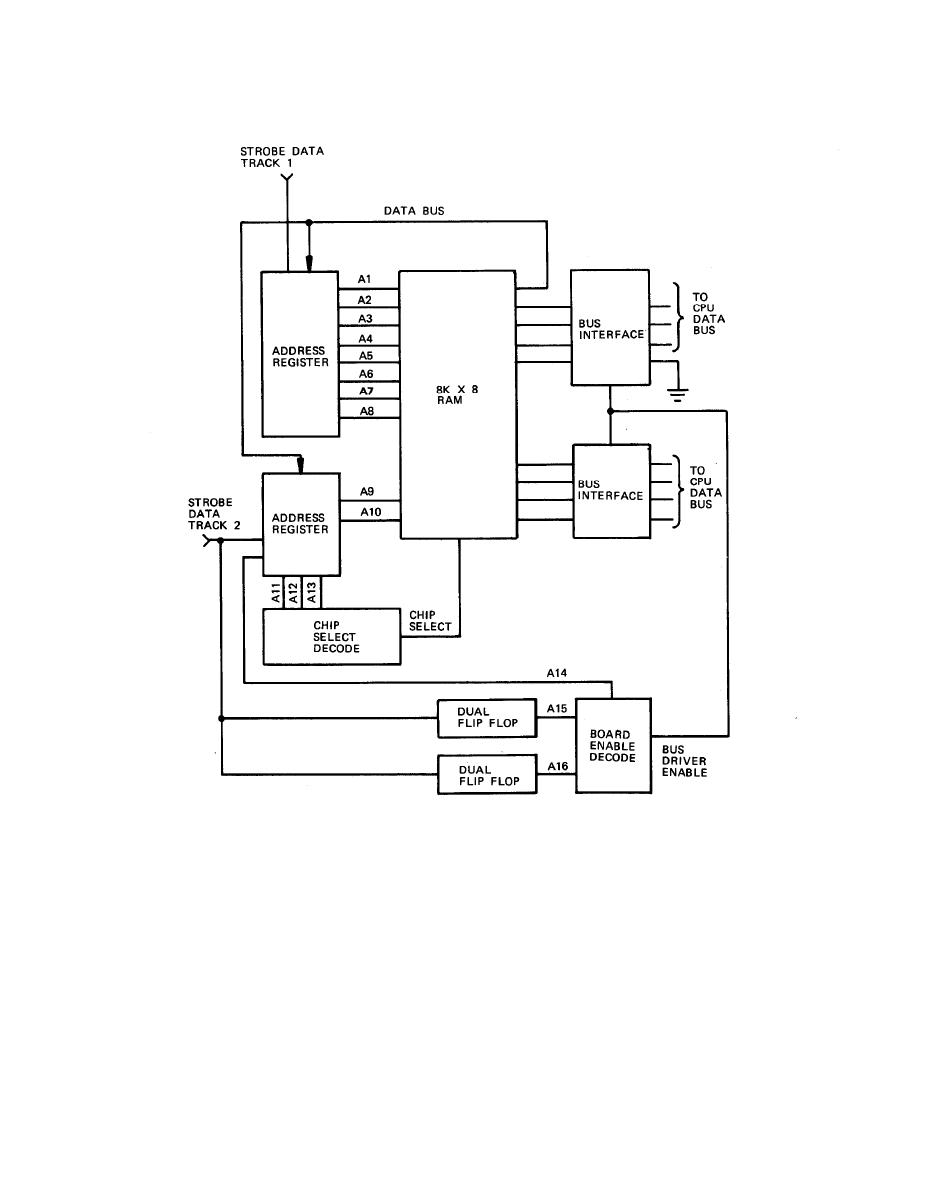

(2) The address register holds the address in memory to be accessed. The

address register is enabled by inputs Strobe Data Track (SDT) 1 and 2. The address

outputs Al thru AlO drive the 8K RAM. Address lines All thru A16 are used for chip

select decoder and board enable decoder. Two bus transceivers interface the 8K RAM

to the CPU data bus. The high-speed transceivers are continuously enabled, and the

bus drivers are gated on by the BDE signal only when data is called for from this

board.

2-49